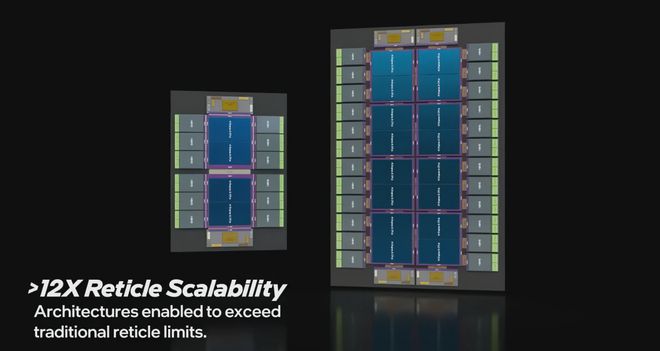

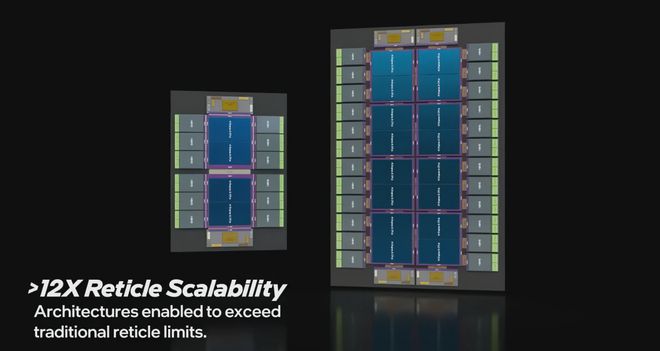

IT之家12月24日报道 科技媒体Wccftech昨日(12月23日)发表博文,报道称英特尔正在展示其在面向高性能计算(HPC)和AI数据中心场景的大规模芯片封装方面的最新成果,能够生产比传统掩模尺寸大12倍的超大型芯片。 Reticle Limit是指芯片制造中光刻机单次曝光的最大面积。突破这一限制(如12x)意味着利用拼接技术打造出比传统单芯片更大的巨型芯片。 IT之家援引博文称,英特尔针对未来计算能力需求,设计并提出了两种概念架构:一种包括 4 个计算模块和 12 个 HBM 内存位置,另一种更为激进,包括 16 个计算模块和 24 个 HBM 内存位置。这些设计表明了英特尔在人工智能和数据中心市场竞争的决心,而不是在远远超过目前的尺寸标准,但直接对标台积电的CoWoS解决方案(目前计划为掩模尺寸的9.5倍)。该包装解决方案采用复杂的 3D 堆叠结构。底层基础晶圆(Base Die)采用Intel 18A-PT工艺制造,引入背面电源技术,提高逻辑密度和供电稳定性。传统芯片从前端为晶体管供电,电路复杂且会干扰信号。背面供电就像将房屋中的所有电线埋在地下,为地下房间(晶体管)留出更多空间来传输数据。基础晶圆中集成了大量的SRAM缓存,其设计类似于“Clearwater Forest”处理器。 Clearwater Forest 基于 18A 处理节点构建,并在其三单元基板解决方案中包含 576 MB 的 L3 缓存。 Clearwater Forest 基板采用 Intel 3 工艺技术制造,因此我们可以预期 Intel 18A-PT进一步优化并增加未来芯片中SRAM的数量。基础Tile之上是主计算Tile,采用Intel 14A或14A-E工艺制作,包含AI引擎或CPU核心。两者通过Foveros Direct 3D技术垂直互连,利用Hybrid Bonding在很小的空间内实现高速通信。为了解决多个芯片之间的通信瓶颈,英特尔部署了下一代EMIB-T(嵌入式多芯片互连桥)技术。该技术引入了硅通孔 (TSV),可显着提高带宽并支持更大规模的模块集成。 IT之家注:EMIB-T相当于在芯片之间搭建了一座“高速三维高架桥”,不仅可以水平连接,还可以通过硅通孔(TSV)进行垂直连接。在存储方面,该方案表现出非常高的兼容性,支持HBM3、HBM4甚至未来的HBM5标准路。顶层芯片设计可容纳多达24个HBM站点,或集成48个LPDDR5x控制器。这种非常高的内存密度将为处理大型人工智能模型和数据中心工作负载提供关键支持。媒体将此次技术展示解读为非致命性的工程能力展示,同时也是Intel Foundry赢得外部客户的重要信号。虽然18A节点主要用于英特尔自己的产品,但14A节点明确设计为面向第三方客户的开放流程。通过展示这种高度可扩展的封装生态系统,英特尔试图证明其在制造和封装领域的领导地位,因为在老桥等项目受挫后,英特尔希望通过 Jaguar Shores 等未来产品和代工订单实现反弹。

特别声明:以上内容(如有,包括照片或视频)由自媒体平台“网易号”用户上传发布。本平台仅提供形成存储服务。

注:以上内容(包括图片和视频,如有)由网易号用户上传发布,网易号为社交媒体平台,仅提供信息存储服务。

手指铸就梦想,美育赋予灵魂――海口海景学校第六届“达美杯”创意实践美术作品现场制作大赛绘成长新篇章

IT之家12月24日报道 科技媒体Wccftech昨日(12月23日)发表博文,报道称英特尔正在展示其在面向高性能计算(HPC)和AI数据中心场景的大规模芯片封装方面的最新成果,能够生产比传统掩模尺寸大12倍的超大型芯片。 Reticle Limit是指芯片制造中光刻机单次曝光的最大面积。突破这一限制(如12x)意味着利用拼接技术打造出比传统单芯片更大的巨型芯片。 IT之家援引博文称,英特尔针对未来计算能力需求,设计并提出了两种概念架构:一种包括 4 个计算模块和 12 个 HBM 内存位置,另一种更为激进,包括 16 个计算模块和 24 个 HBM 内存位置。这些设计表明了英特尔在人工智能和数据中心市场竞争的决心,而不是在远远超过目前的尺寸标准,但直接对标台积电的CoWoS解决方案(目前计划为掩模尺寸的9.5倍)。该包装解决方案采用复杂的 3D 堆叠结构。底层基础晶圆(Base Die)采用Intel 18A-PT工艺制造,引入背面电源技术,提高逻辑密度和供电稳定性。传统芯片从前端为晶体管供电,电路复杂且会干扰信号。背面供电就像将房屋中的所有电线埋在地下,为地下房间(晶体管)留出更多空间来传输数据。基础晶圆中集成了大量的SRAM缓存,其设计类似于“Clearwater Forest”处理器。 Clearwater Forest 基于 18A 处理节点构建,并在其三单元基板解决方案中包含 576 MB 的 L3 缓存。 Clearwater Forest 基板采用 Intel 3 工艺技术制造,因此我们可以预期 Intel 18A-PT进一步优化并增加未来芯片中SRAM的数量。基础Tile之上是主计算Tile,采用Intel 14A或14A-E工艺制作,包含AI引擎或CPU核心。两者通过Foveros Direct 3D技术垂直互连,利用Hybrid Bonding在很小的空间内实现高速通信。为了解决多个芯片之间的通信瓶颈,英特尔部署了下一代EMIB-T(嵌入式多芯片互连桥)技术。该技术引入了硅通孔 (TSV),可显着提高带宽并支持更大规模的模块集成。 IT之家注:EMIB-T相当于在芯片之间搭建了一座“高速三维高架桥”,不仅可以水平连接,还可以通过硅通孔(TSV)进行垂直连接。在存储方面,该方案表现出非常高的兼容性,支持HBM3、HBM4甚至未来的HBM5标准路。顶层芯片设计可容纳多达24个HBM站点,或集成48个LPDDR5x控制器。这种非常高的内存密度将为处理大型人工智能模型和数据中心工作负载提供关键支持。媒体将此次技术展示解读为非致命性的工程能力展示,同时也是Intel Foundry赢得外部客户的重要信号。虽然18A节点主要用于英特尔自己的产品,但14A节点明确设计为面向第三方客户的开放流程。通过展示这种高度可扩展的封装生态系统,英特尔试图证明其在制造和封装领域的领导地位,因为在老桥等项目受挫后,英特尔希望通过 Jaguar Shores 等未来产品和代工订单实现反弹。

特别声明:以上内容(如有,包括照片或视频)由自媒体平台“网易号”用户上传发布。本平台仅提供形成存储服务。

注:以上内容(包括图片和视频,如有)由网易号用户上传发布,网易号为社交媒体平台,仅提供信息存储服务。

手指铸就梦想,美育赋予灵魂――海口海景学校第六届“达美杯”创意实践美术作品现场制作大赛绘成长新篇章

IT之家12月24日报道 科技媒体Wccftech昨日(12月23日)发表博文,报道称英特尔正在展示其在面向高性能计算(HPC)和AI数据中心场景的大规模芯片封装方面的最新成果,能够生产比传统掩模尺寸大12倍的超大型芯片。 Reticle Limit是指芯片制造中光刻机单次曝光的最大面积。突破这一限制(如12x)意味着利用拼接技术打造出比传统单芯片更大的巨型芯片。 IT之家援引博文称,英特尔针对未来计算能力需求,设计并提出了两种概念架构:一种包括 4 个计算模块和 12 个 HBM 内存位置,另一种更为激进,包括 16 个计算模块和 24 个 HBM 内存位置。这些设计表明了英特尔在人工智能和数据中心市场竞争的决心,而不是在远远超过目前的尺寸标准,但直接对标台积电的CoWoS解决方案(目前计划为掩模尺寸的9.5倍)。该包装解决方案采用复杂的 3D 堆叠结构。底层基础晶圆(Base Die)采用Intel 18A-PT工艺制造,引入背面电源技术,提高逻辑密度和供电稳定性。传统芯片从前端为晶体管供电,电路复杂且会干扰信号。背面供电就像将房屋中的所有电线埋在地下,为地下房间(晶体管)留出更多空间来传输数据。基础晶圆中集成了大量的SRAM缓存,其设计类似于“Clearwater Forest”处理器。 Clearwater Forest 基于 18A 处理节点构建,并在其三单元基板解决方案中包含 576 MB 的 L3 缓存。 Clearwater Forest 基板采用 Intel 3 工艺技术制造,因此我们可以预期 Intel 18A-PT进一步优化并增加未来芯片中SRAM的数量。基础Tile之上是主计算Tile,采用Intel 14A或14A-E工艺制作,包含AI引擎或CPU核心。两者通过Foveros Direct 3D技术垂直互连,利用Hybrid Bonding在很小的空间内实现高速通信。为了解决多个芯片之间的通信瓶颈,英特尔部署了下一代EMIB-T(嵌入式多芯片互连桥)技术。该技术引入了硅通孔 (TSV),可显着提高带宽并支持更大规模的模块集成。 IT之家注:EMIB-T相当于在芯片之间搭建了一座“高速三维高架桥”,不仅可以水平连接,还可以通过硅通孔(TSV)进行垂直连接。在存储方面,该方案表现出非常高的兼容性,支持HBM3、HBM4甚至未来的HBM5标准路。顶层芯片设计可容纳多达24个HBM站点,或集成48个LPDDR5x控制器。这种非常高的内存密度将为处理大型人工智能模型和数据中心工作负载提供关键支持。媒体将此次技术展示解读为非致命性的工程能力展示,同时也是Intel Foundry赢得外部客户的重要信号。虽然18A节点主要用于英特尔自己的产品,但14A节点明确设计为面向第三方客户的开放流程。通过展示这种高度可扩展的封装生态系统,英特尔试图证明其在制造和封装领域的领导地位,因为在老桥等项目受挫后,英特尔希望通过 Jaguar Shores 等未来产品和代工订单实现反弹。

特别声明:以上内容(如有,包括照片或视频)由自媒体平台“网易号”用户上传发布。本平台仅提供形成存储服务。

注:以上内容(包括图片和视频,如有)由网易号用户上传发布,网易号为社交媒体平台,仅提供信息存储服务。

手指铸就梦想,美育赋予灵魂――海口海景学校第六届“达美杯”创意实践美术作品现场制作大赛绘成长新篇章

推荐文章

推荐文章